# F4164 65,536 x 1 Dynamic RAM

MOS Memory Products

Description

The F4164 is a dynamic Random Access Memory (RAM) circuit organized as 65,536 single-bit words. This memory uses the Fairchild advanced double poly NMOS, Isoplanar-H™ process which allows volume manufacture of reliable, high density memory products.

Innovative architecture and circuit design provide significant user benefits including wide operating margins, low power dissipation and excellent noise characteristics. Double cruciform architecture minimizes signal path lengths to improve noise margin and reduce propagation delays. A multiplexed sense amplifier scheme halves the number of sense amplifiers and the bit-line to cell capacitance ratio; this simultaneously reduces power consumption and improves signal sensing margins. Full-sized reference cells provide good margins and control. Low capacitance TTL-compatible inputs with overshoot and anti-static protection insure data and address input integrity.

- INDUSTRY STANDARD 16-PIN DIP WITH PIN 1

NOT CONNECTED (NC)

- LOW CAPACITANCE TTL-COMPATIBLE INPUTS WITH OVERSHOOT AND ANTI-STATIC PROTECTION

- COMMON I/O CAPABILITY

- STANDARD 5 V ± 10% SINGLE POWER SUPPLY REQUIREMENT

- LOW POWER 209 mW ACTIVE (MAX) 19.3 mW STANDBY (MAX)

- FAST ACCESS TIME 120 ns, 150 ns or 200 ns

- READ-MODIFY-WRITE, RAS-ONLY REFRESH AND PAGE MODE CAPABILITY

- OUTPUT UNLATCHED AT CYCLE END ALLOWS FOR PAGE BOUNDARY EXTENSION AND TWO-DIMENSIONAL CHIP SELECTION

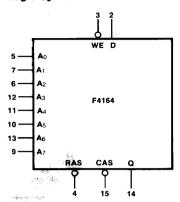

## Pin Names

A<sub>O</sub>-A<sub>7</sub> Address Inputs

RAS Row Address Strobe

CAS Column Address Strobe

WE Write Enable

D Data Input

Q Data Output

#### Logic Symbol

V<sub>SS</sub> = Pin 16 V<sub>DD</sub> = Pin 8

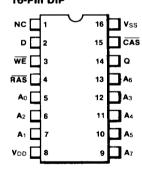

#### Connection Diagram 16-Pin DIP

(Top View)

| Package     | Outline | Order<br>Code |

|-------------|---------|---------------|

| Ceramic DIP | WC      | D             |

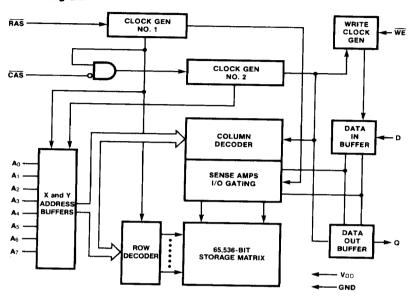

#### **Block Diagram**

#### **Functional Description**

# **Memory Cycles**

The F4164 operates in several modes which reflect various application considerations, some examples of which follow.

# Random Read or Write Cycle

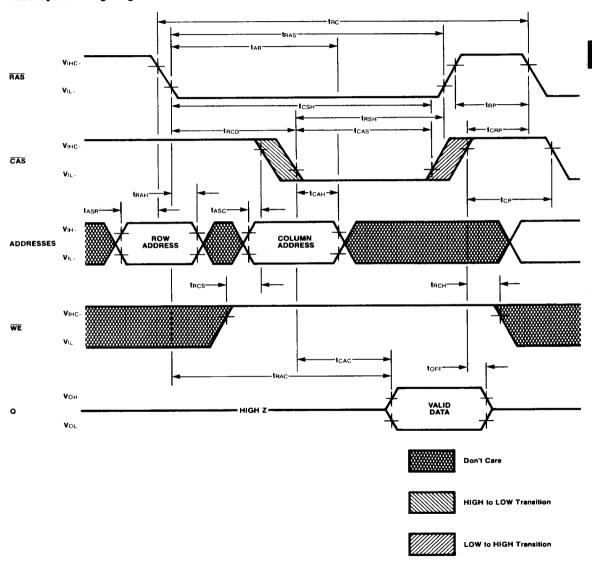

This mode implements standard Read or Write operation. Addresses are entered in two consecutive 8-bit bytes synchronized with RAS and CAS. In the Read case, WE should be HIGH before the falling edge of CAS. During Early-Write operations, WE falls before CAS, causing the output to remain in the high impedance state. This output mode is useful if the RAM Data input (D) and Data output (Q) pins are to be wired in common as a bidirectional data bus.

#### Read-Write Cycle

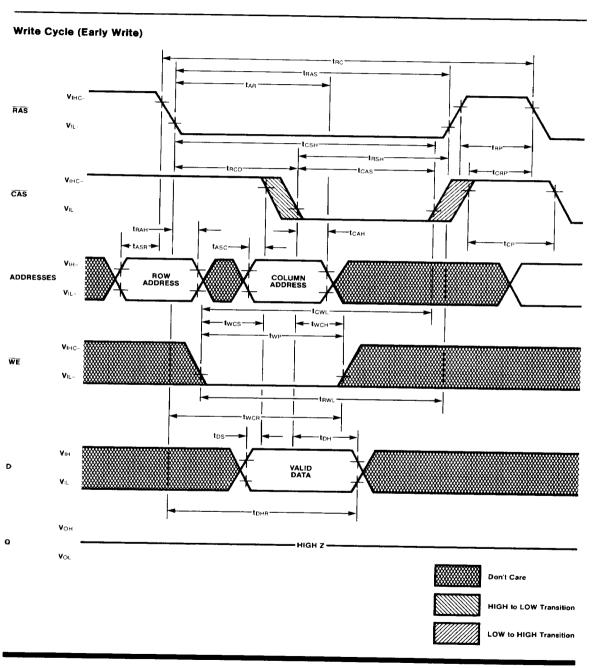

The Read-Write mode is used when new data is to be written into the same cell location from which the content is currently being read. Since no address change is required, this mode provides a much faster Read-Write cycle by allowing the overhead associated with the address decoder and precharge

to be amortized over two operations. In general,  $t_{RWC}$  is significantly less than twice  $t_{RC}$ . In this mode the new input data is not a function of the currently stored data. For that reason the cycle time is not limited by access time ( $t_{RAC}$ ), but by Write considerations such as  $t_{RWD}$  and  $t_{RWL}$ .

# Read-Modify-Write Cycle

The Read-Modify-Write cycle is used when the data from the cell at the current address is used to derive new data for writing back into that cell, such as in error correction schemes. In this mode, cycle time is dependent upon both read access time and write-related parameters.

#### Addressing

The 16 address bits required to decode one-of-65,536 storage cell locations in the F4164 are entered using a two-phase multiplexing operation. First, the 8-bit row address is applied to the eight Address inputs of the F4164 and latched into the chip by Row Address Strobe (RAS). Next, the 8-bit column address is presented to the Address inputs and latched by the Column Address Strobe (CAS). All addresses must be stable on or before the falling edge of RAS or CAS.

CAS is internally inhibited by a signal derived from RAS. This feature prevents column addresses from being strobed onto the chip before row address dependent operations have been completed.

The gated- $\overline{CAS}$  feature allows  $\overline{CAS}$  to occur any time before  $t_{RCD(max)}$  with no effect on the worst-case access time  $(t_{RAC})$ . No errors will result if  $\overline{CAS}$  is applied to the F4164 after the  $t_{RCD(max)}$  limit, but access time will then be determined from  $\overline{CAS}$  ( $t_{CAC}$ ) rather than from  $\overline{RAS}$  ( $t_{RAC}$ ).

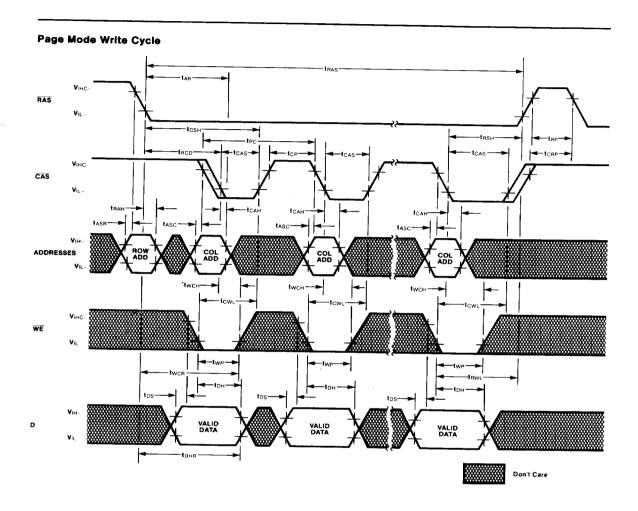

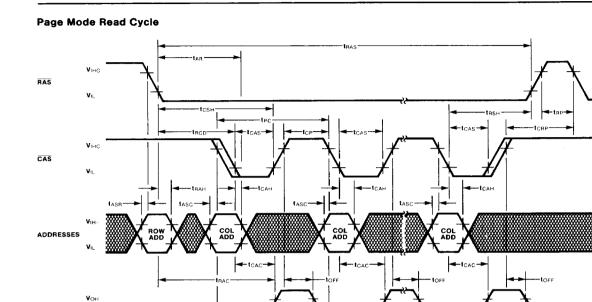

#### Page Mode Operation

Higher speed and lower power operations can be performed in Page Mode on bits sharing a Row Address. In this mode RAS strobes in the common Row Address and is then kept LOW (active) while successive CAS cycles allow the required Column Addresses to be strobed in for subsequent Read or Write operations. Data from the first bit addressed is accessed within tRAC (or tRCD + tCAC if tRCD > tRCD(max)) and subsequent Column Addresses are accessed within tCAC only.

Both the delays and the dynamic power dissipation associated with row selection and sensing occur only once with the initial RAS transition. Thereafter, delays and dynamic power dissipation are incurred only in the column select and data path. The delay and power in the row and sensing circuitry are amortized over 256 different Column Addresses offering improved speed and lower power per bit.

Page Mode <u>address</u> boundaries may be extended by multiplexing <u>CAS</u> to several devices which share a common Data output (Q) bus.

#### **Data Input**

In a Write operation, the data to be written is latched into the chip while RAS is LOW by a combination of CAS and Write Enable (WE). The strobe is enabled by the last of these two signals to go LOW. This allows several types of write cycles to be performed. In an Early-Write cycle (WE LOW before CAS goes LOW), the Data input (D) is strobed by CAS. Here data set-up and hold times are referenced to CAS. If D is not yet valid at the time CAS becomes active, or if a Read-Write or Read-Modify-Write cycle is desired, then WE must be delayed. In this "late-write" mode, the data set-up and hold times are referenced to WE rather than CAS.

#### **Data Output**

The Data output (Q) buffer assumes a high impedance state whenever CAS is HIGH (inactive) subject to tOFF(max). If the cycle being performed is a Read, Read-Modify-Write, or a "late-write" cycle, then the Q latch and buffer will remain high impedance until the access time, after which Q will assume the value of the data read from the selected cell. This output data is of the same polarity as the input data and will remain valid as long as CAS is kept LOW (active). However, if the operation is an Earty-Write, or if the chip does not receive both RAS and CAS, then Q will remain high impedance throughout the cycle. This feature allows systems which write exclusively in the Early-Write mode to connect D and Q directly together.

Since both RAS and CAS must be supplied for a device to be "active", a reduction in external decoding logic can be realized by using RAS and CAS in a 2-dimensional decoding/selection scheme. An analogous method can be used to extend the page boundary to beyond 256 locations by decoding which device receives a CAS in addition to the RAS already latched into the chips. Only those devices which receive both RAS and CAS will respond with a valid memory cycle (see Table 1).

#### Table 1 RAS and CAS Clock Conditions

| RAS and CAS cycle   | Device active              |

|---------------------|----------------------------|

| RAS-only cycle      | Device deselected, refresh |

| CAS-only cycle      | Device deselected          |

| Neither RAS nor CAS | Device deselected, standby |

#### Refresh

Refresh of the data stored in the dynamic cell matrix of the F4164 is accomplished by performing a memory cycle at each of the 256 row addresses at least every 4 ms. Performing a RAS-only Refresh with CAS held HIGH causes the output buffer to remain in the high-impendence state throughout the cycle.

The F4164 256-cycle, 4 ms refresh timing requirement is compatible with distributed refresh techniques currently utilized for 128-cycle, 2 ms refresh 16K dynamic RAMs.

# Absolute Maximum Ratings

Voltage on Any Pin with Respect

to V<sub>SS</sub> V<sub>DD</sub> Supply with Respect to V<sub>SS</sub>

Storage Temperature

Power Dissipation

Short-Circuit Output Current Operating Temperature -1.0 V to +7.0 V -1.0 V to +7.0 V

-65°C to +150°C

50 mA 0°C to +70°C Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# Recommended Operating Conditions (Note)

| Symbol            | Characteristic                | Min  | Тур | Max | Unit |

|-------------------|-------------------------------|------|-----|-----|------|

| V <sub>DD</sub>   | Supply Voltage                | 4.5  |     | 5.5 | V    |

| SS Supply Voltage | 0                             |      | 0   | V   |      |

| VIH               | Input HIGH Voltage            | 2.4  |     | 6.5 | tv   |

| VIL               | Input LOW Voltage, All Inputs | -1.0 |     | 0.8 | V    |

# DC Characteristics Recommended operating conditions unless otherwise noted.

| Symbol           | Characteristic                                       | Min | Тур | Max | Unit | Condition                                                                                                             |  |  |

|------------------|------------------------------------------------------|-----|-----|-----|------|-----------------------------------------------------------------------------------------------------------------------|--|--|

| VoL              | Output LOW Voltage                                   |     |     | 0.4 | V    | I <sub>OL</sub> = 4.2 mA                                                                                              |  |  |

| V <sub>OH</sub>  | Output HIGH Voltage                                  | 2.4 |     |     | v    | I <sub>OH</sub> = -5.0 mA                                                                                             |  |  |

| I <sub>DD1</sub> | Operating Current Average<br>Power Supply Current    |     | 27  | 38  | mA   | RAS, CAS cycling; t <sub>RC</sub> = Min<br>Q = no connection                                                          |  |  |

| I <sub>DD2</sub> | Standby Current<br>Power Supply Current              |     |     | 3.5 | mA   | RAS = CAS = V <sub>IH</sub>                                                                                           |  |  |

| IDDЗ             | Refresh Current Average<br>Power Supply Current      |     | 21  | 32  | mA   | RAS cycling, CAS = V <sub>IH</sub> ,<br>t <sub>RC</sub> = Min, Q = no connection                                      |  |  |

| l <sub>DD4</sub> | Page Mode Current<br>Average Power<br>Supply Current |     | 15  | 30  | mA   | RAS = V <sub>IL</sub> , CAS cycling,<br>t <sub>CP</sub> = Min, Q = no connection                                      |  |  |

| lıL              | Input Leakage Current                                | -10 |     | 10  | μА   | Any Input, $0 \text{ V} \leq \text{V}_{\text{IN}} \leq 6.5 \text{ V}$ ; all other pins not under test = $0 \text{ V}$ |  |  |

| lor              | Output Leakage Current                               | -10 |     | 10  | μΑ   | Data Out is disabled,<br>0 V ≤ V <sub>OUT</sub> ≤ 6.5 V                                                               |  |  |

# Capacitance $T_A = +25$ °C

| Symbol           | Characteristic                                       | Min | Тур | Max | Unit |

|------------------|------------------------------------------------------|-----|-----|-----|------|

| CIN 1            | input Capacitance A <sub>0</sub> -A <sub>7</sub> , D |     |     | 5.0 | pF   |

| C <sub>IN2</sub> | Input Capacitance RAS, CAS, WE                       |     |     | 10  | DF   |

| Cour             | Output Capacitance Q                                 |     |     | 7.0 | pF   |

#### Note

All Voltages are referenced to VSS. Conditions apply over the entire operating temperature range.

F4164

AC Characteristics Recommended operating conditions unless otherwise noted (Notes 1, 2, and 3)

|                               |                 |                                               | F4164-1 |     | F4164-2 |     | F4164-3 |     |      |      |

|-------------------------------|-----------------|-----------------------------------------------|---------|-----|---------|-----|---------|-----|------|------|

| IEEE<br>Symbol <sup>(9)</sup> | Symbol          | Characteristic                                | Min     | Max | Min     | Max | Min     | Max | Unit | Note |

| TRVRV                         | tREF            | Time between Refresh                          |         | 4.0 |         | 4.0 |         | 4.0 | ms   |      |

| TRELREL                       | tRC             | Random Read/Write Cycle Time                  | 300     |     | 320     |     | 330     |     | ns   |      |

| TRELREL                       | tRWC            | Read-Write Cycle Time                         | 315     |     | 335     |     | 375     |     | ns   |      |

| TCELCEL                       | tPC             | Page Mode Cycle Time                          | 160     |     | 170     |     | 225     |     | ns   |      |

| TRELQV                        | tRAC            | Access Time from RAS                          |         | 120 |         | 150 |         | 200 | ns   | 4, 6 |

| TCEHQV                        | tCAC            | Access Time from CAS                          |         | 80  |         | 100 |         | 135 | ns   | 5, 6 |

| TCEHQZ                        | toff            | Output Buffer Turn-Off Delay                  | 0       | 35  | 0       | 40  | 0       | 50  | กร   |      |

| TT                            | tŢ              | Transition Time                               | 3.0     | 35  | 3.0     | 35  | 3.0     | 50  | ns   |      |

| TREHREL                       | tRP             | RAS Precharge Time                            | 80      |     | 100     |     | 120     |     | ns   |      |

| TRELREH                       | tRAS            | RAS Pulse Width                               | 120     | 10K | 150     | 10K | 200     | 10K | ns   |      |

| TCELREH                       | trsh            | RAS Hold Time                                 | 80      |     | 100     |     | 135     |     | ns   |      |

| TCEHCEL                       | tCP             | CAS Precharge Time                            | 60      |     | 60      |     | 80      |     | ns   |      |

| TCELCEH                       | tCAS            | CAS Pulse Width                               | 80      | 10K | 100     | 10K | 135     | 10K | ns   |      |

| TRELCEH                       | tcsн            | CAS Hold Time                                 | 120     |     | 150     |     | 200     |     | ns   |      |

| TRELCEL                       | tRCD            | RAS to CAS Delay Time                         | 25      | 40  | 30      | 50  | 35      | 65  | ns   | 7    |

| TCEHREL                       | tCRP            | CAS to RAS Precharge Time                     | 0       |     | 0       |     | 0       |     | ns   |      |

| TARVREL                       | tasa            | Row Address Set-up Time                       | 0       |     | 0       |     | 0       |     | ns   |      |

| TRELARX                       | tRAH            | Row Address Hold Time                         | 15      |     | 20      |     | 25      |     | ns   |      |

| TACVCEL                       | tASC            | Column Address Set-up Time                    | 0       |     | 0       |     | 0       |     | ns   |      |

| TCELACX                       | tCAH            | Column Address Hold Time                      | 40      |     | 45      |     | 55      | T   | ns   |      |

| TRELACX                       | t <sub>AR</sub> | Column Address Hold Time<br>Referenced to RAS | 80      |     | 95      |     | 120     |     | ns   |      |

| TWHCEL                        | tRCS            | Read Command Set-up Time                      | 0       |     | 0       |     | 0       |     | ns   |      |

| TCEHWL                        | tRCH            | Read Command Hold Time                        | 0       |     | 0       |     | 0       |     | ns   |      |

| TWLCEL                        | twcs            | Write Command Set-up Time                     | 0       |     | -10     |     | -10     |     | ns   | 8    |

| TCELWH                        | twch            | Write Command Hold Time                       | 40      |     | 45      |     | 55      |     | ns   |      |

| TRELWH                        | twcR            | Write Command Hold Time<br>Reference to RAS   | 80      |     | 95      |     | 120     |     | ns   |      |

| TWLWH                         | twp             | Write Command Pulse Width                     | 40      |     | 45      |     | 55      |     | ns   |      |

| TWLREH                        | tRWL            | Write Command to RAS Lead Time                | 60      |     | 70      |     | 80      |     | ns   |      |

| TWLCEH                        | tcwL            | Write Command to CAS Lead Time                | 60      |     | 70      |     | 80      |     | ns   |      |

Notes on following page.

### AC Characteristics (Continued)

| IEEE<br>Symbol <sup>(9)</sup> |                  |                                        | F4164-1 |                                                  | F4164-2 |                                                  | F4164-3 |                                                  | T    | T              |

|-------------------------------|------------------|----------------------------------------|---------|--------------------------------------------------|---------|--------------------------------------------------|---------|--------------------------------------------------|------|----------------|

|                               | Symbol           | Characteristic                         | Min     | Max                                              | Min     | Max                                              | Min     | Max                                              | Unit | Note           |

| TDVREL                        | tDS              | Data in Set-up Time                    | o       | <b>—</b>                                         | 0       | †                                                | 0       |                                                  | ns   | 1              |

| TCELDX                        | tDH              | Data In Hold Time                      | 40      | $\dagger$                                        | 45      | +                                                | 55      | +                                                | ns   | <del> </del> - |

| TRELDX                        | <sup>†</sup> DHR | Data In Hold Time<br>Referenced to RAS | 80      |                                                  | 95      |                                                  | 120     |                                                  | ns   |                |

| TCELWL                        | tcwp             | CAS to WE Delay                        | 60      | T                                                | 70      |                                                  | 95      | +                                                | ns   | 8              |

| TRELWL                        | tRWD             | RAS to WE Delay                        | 100     | <del>                                     </del> | 120     | <del>                                     </del> | 160     | <del>                                     </del> | ns   | 8              |

#### Notes

- Several cycles are required after power up before proper device operation is achieved. Any eight cycles which perform refresh are adequate for this purpose.

- 2. Dynamic measurements assume  $t_T = 5$  ns.

- V<sub>IH</sub>(min) and V<sub>IL</sub>(max) are reference levels for measuring timing of input signals. Also, transition times are measured between V<sub>IH</sub> and V<sub>II</sub>.

- Assumes that t<sub>RCD</sub> ≤ t<sub>RCD(max)</sub>. If t<sub>RCD</sub> is greater than the maximum recommended value shown in this table, t<sub>RAC</sub> will increase by the amount that t<sub>RCD</sub> exceeds the value shown.

- Assumes that t<sub>RCD</sub> ≥ t<sub>RCD(max)</sub>.

- 6. Refer to test conditions.

- Operation within the t<sub>RCD(max)</sub> limit insures that t<sub>RAC(max)</sub> can be met. t<sub>RCD(max)</sub> is specified as a reference point only; if t<sub>RCD</sub> is greater than the specified t<sub>RCD(max)</sub> limit, then access time is controlled exclusively by t<sub>CAC</sub>.

- 8. tWCs. tCWD and tRWD are restrictive operating characteristics due to the following. If tWCs ≥ tWCs(min), the cycle is an early write cycle and the Data output pin will be open circuit (high impedance) throughout the entire cycle. If tCWD ≥ tCWD(min) and tRWD ≥ tRWD(min), the cycle is a read-write cycle and Data output will contain data read from the selected cell. If neither of the conditions is satisfied the condition of the Data output is indeterminate.

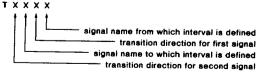

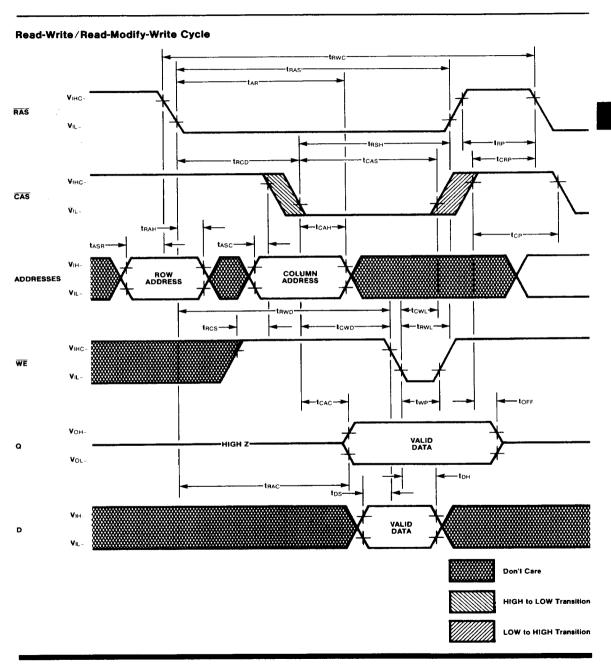

- 9. Timing Parameter Abbreviations

All timing abbreviations in this format use upper case characters with no subscripts. The initial character is always T and is followed by four descriptors. These characters specify two signal points arranged in a 'from-to' sequence that define a timing interval. The two descriptors for each signal point specify the signal name and the signal transitions. Thus the format is:

The signal definitions used in this data sheet are:

RE = RAS. CE = CAS

AR = Row Address

AC = Column Address

A = Address

D = Data in

Q = Data Out

W = Write Enable

The transition definitions used in this data sheet are:

H = transition to HIGH

L = transition to LOW

V = transition to valid

X = transition to invalid or don't care

Z = transition to off (high impedance)

#### **Timing Limits**

The table of timing values shows either a minimum or a maximum limit for each parameter. Input requirements are specified from the external system point of view. Thus, address set-up time is shown as a minimum since the system must supply at least that much time (even though most devices do not require it). On the other hand, responses from the memory are specified from the device point of view. Thus, the access time is shown as a maximum since the device never provides data later than that time.

# **Timing Diagrams**

# **Read Cycle Timing Diagram**

3-45

# #RAS-only" Refresh Cycle ViHC RAS VIL. ADDRESSES VIL. ROW ADDRESS ADDRESS

- HIGH Z -

VOH-

VOL-

Don't Care

3-47

HIGH Z

Vοι